|

Fujitsu and University of Toronto Develop World's Lowest Power Referenceless CDR for Optical Modules

Contributing to improved processing capability in datacenters through miniaturizing and saving power in optical modules

KAWASAKI, Japan, Feb 07, 2017 - (JCN Newswire) - The University of Toronto and Fujitsu Laboratories Ltd. today announced joint development of the world's lowest power referenceless CDR(1). The newly developed circuit operates with 55% of the power requirements of previous technology for optical modules in Ethernet used for communication between servers and switches in datacenters.

With the spread of big data analysis and cloud services, there has been a demand for faster and denser optical modules in order to provide high data transfer capability between servers and switches, which has necessitated miniaturization and reductions in power consumption.

To speed up and miniaturize optical modules, referenceless CDR technology has been developed that does not require a crystal oscillator to produce the standard timing. With existing referenceless CDRs, however, the circuit that detects discrepancies in the timing cycle for reading input data has high power consumption, leading to problematic heat generation and causing difficulties in increasing circuit density.

Previously, in order to detect discrepancies in the data-reading cycle, it was necessary to detect the signal four times with different timing for each bit of data, with the power consumption for each timing generator taking up a significant proportion of the power consumption of the module as a whole. Now, the University of Toronto and Fujitsu Laboratories have developed a new timing extraction technology that can operate on the same cycle as the data transmission speed, detecting once for each bit discrepancies in the reading cycle from amplitude information in the input signal. The result is that the number of timing generators can be reduced to one-fourth that of previous architectures, successfully cutting power consumed by the optical module as a whole to about 70% that of previous technologies.

This technology lowers the power consumption of optical modules, enabling high traffic transmission capability through denser implementations and thereby improving datacenter processing capability.

Details of this technology will be announced at the IEEE International Solid-State Circuits Conference 2017, which is the largest conference for semiconductor technology, being held from February 5 in San Francisco (ISSCC session numbers 6.6)

Development Background

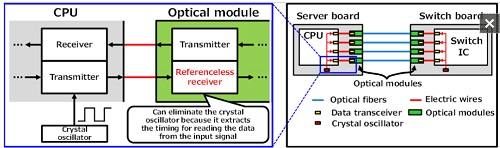

| | Figure 1: Structure of the connection between a CPU and an optical module using referenceless CDRs | | |

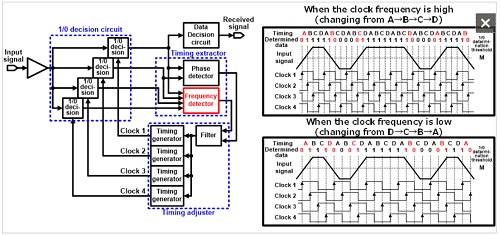

| | Figure 2: Architecture of existing referenceless CDR and frequency difference detection | | |

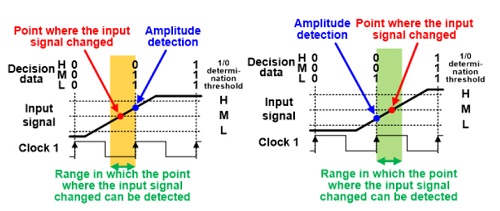

| | Figure 3: Timing detection method | | |

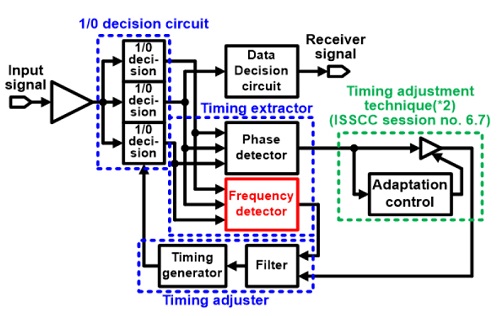

| | Figure 4: New referenceless CDR architecture | | |

With the spread of big data analysis and cloud services, there is a demand for high data transfer capability between servers and each switch. For this reason, there is a demand for higher speed, greater miniaturization, and higher density implementations for the optical modules used in communication between servers and switches.

Issues

Reducing the number of components in optical modules is an effective way to reduce the power consumption and improve miniaturization. For this reason, referenceless CDRs, which do not require a standard timing (reference), are used to enable the elimination of the crystal oscillator.

The circuits that regulate the observation of the input signal and the reading of data in existing referenceless CDRs, however, must operate at high speed, leading to high power consumption, as well as difficulties in high density installation due to heat that accompanies this power consumption.

http://www.acnnewswire.com/topimg/Low_FujitsuCDRFig1.jpg

Figure 1: Structure of the connection between a CPU and an optical module using referenceless CDRs

With existing referenceless CDR architectures, the CDR decides whether each bit of data is a 1 or a 0 four times, and the data-reading cycle is regulated by observing changes in the results of each decision.

The input signal is observed with respect to clocks 1 through 4-generated by the timing generators- as it changes from 0 to 1, and each bit is assigned a 1 or a 0. This makes it possible to observe between which two clocks the data changed from 0 to 1 or vice versa. For example, as shown in Fig. 2, when the crossover point is observed to change from A-B-C-D, it can be understood that the data-reading cycle is shorter than the input signal. If the opposite change, from D-C-B-A, is observed, it can be understood that the data-reading cycle is longer than the input signal.

http://www.acnnewswire.com/topimg/Low_FujitsuCDRFig2.jpg

Figure 2: Architecture of existing referenceless CDR and frequency difference detection

About the Technology

Now, Fujitsu Laboratories and the University of Toronto have developed technology that reduces the power consumption of referenceless CDRs by using a new method to detect discrepancies in the data-reading cycle from the amplitude information of the input signal.

With this technology, in order to detect discrepancies in the data-reading cycle from amplitude information, three decision circuits with different threshold levels (low, medium, and high) determining whether the input signal is a 0 or a 1, all operate at the same timing to investigate the change in the input signal. For example, when the input signal changes from 0 to 1, if the three results determined by the timing of clock 1 are "0,1,1", then it can be determined that the point at which the input signal changed is earlier than the determination timing of clock 1 (yellow area in Fig. 3), while if the results are "0,0,1", then it can be determined that the point at which the input signal changed is later than the determination timing of clock 1 (green area in Fig. 3). Then, by investigating how that timing is changing, timing discrepancies can be detected.

With this technology, it becomes possible to reduce the number of timing generators to one fourth that of previous architectures (Fig. 4).

http://www.acnnewswire.com/topimg/Low_FujitsuCDRFig3.jpg

Figure 3: Timing detection method

http://www.acnnewswire.com/topimg/Low_FujitsuCDRFig4.jpg

Figure 4: New referenceless CDR architecture

Effects

With this newly developed technology, the power consumption of referenceless CDRs can be reduced to 55% that of previous architectures, cutting power consumption of optical modules to 70%. This means it is now possible to implement optical modules in higher densities than before. This is expected to contribute greatly to improving the performance of datacenters.

Future Plans

Fujitsu Laboratories is aiming for the commercialization of this newly-developed technology in fiscal 2019.

(1) Referenceless CDR

Clock and data recovery circuit. A type of receiver used in data transmission which extracts timing information (clock data) from the received data, without using a high-accuracy reference signal to generate the timing information needed to determine if the received data is a 0 or a 1.

(2) Timing adjustment technology

The University of Toronto and Fujitsu Laboratories have also developed a timing adjustment technology (ISSCC session number 6.7) to improve the reliability of receivers in response to the influence of changes in temperature or noise. This offers highly reliable receivers that are independent from environmental changes.

About The Edward S. Rogers Sr. Department of Electrical & Computer Engineering at the University of Toronto

Founded in 1909, The Edward S. Rogers Sr. Department of Electrical & Computer Engineering (ECE) at the University of Toronto maintains a proud history of innovative education and world-leading research. We are the top-ranked ECE department in Canada and among the best in the world. Our strong emphasis on teaching excellence means both undergraduate and graduate students learn from professors who are international leaders in their fields, in a vibrant and diverse environment. ECE graduates become leaders in every possible field, from mobile to medicine, energy to entertainment. For more on our degree programs, research and events, visit www.ece.utoronto.ca

About Fujitsu Laboratories

Founded in 1968 as a wholly owned subsidiary of Fujitsu Limited, Fujitsu Laboratories Ltd. is one of the premier research centers in the world. With a global network of laboratories in Japan, China, the United States and Europe, the organization conducts a wide range of basic and applied research in the areas of Next-generation Services, Computer Servers, Networks, Electronic Devices and Advanced Materials. For more information, please see: http://www.fujitsu.com/jp/group/labs/en/.

Contact:University of Toronto

E-mail: ali@ece.utoronto.ca

Fujitsu Laboratories Ltd.

E-mail: hsio2017@ml.labs.fujitsu.com

Fujitsu Limited

Public and Investor Relations

Tel: +81-3-3215-5259

URL: www.fujitsu.com/global/news/contacts/

Source: Fujitsu Ltd

Sectors: Electronics

Copyright ©2024 JCN Newswire. All rights reserved. A division of Japan Corporate News Network. |

Latest Press Release

JCB enables JCB Contactless acceptance at Taichung MRT in Taiwan

Apr 26, 2024 10:00 JST

|

Mazda Production and Sales Results for March 2024 and for April 2023 through March 2024

Apr 25, 2024 18:21 JST

|

MHI Begins Operation of SOEC Test Module the Next-Generation High-Efficiency Hydrogen Production Technology at Takasago Hydrogen Park

Apr 25, 2024 17:45 JST

|

GAC Honda to Begin Sales of All-new e:NP2, the Second Model of e:N Series

Apr 25, 2024 16:50 JST

|

Toyota Exhibiting at Beijing Motor Show 2024

Apr 25, 2024 16:25 JST

|

Honda Reaches Basic Agreement with Asahi Kasei on Collaboration for Production of Battery Separators for Automotive Batteries in Canada

Apr 25, 2024 11:10 JST

|

UNIQLO Sponsors KAWS + Warhol Exhibition Tour, Starting in Pittsburgh

Apr 25, 2024 09:00 JST

|

Mitsubishi Power Begins Commercial Operation of Seventh M701JAC Gas Turbine in Thailand GTCC Project; Achieves 75,000 AOH To-Date

Apr 24, 2024 17:19 JST

|

MC and Denka Sign J/V Agreement in Fullerene Business

Apr 24, 2024 17:02 JST

|

Mitsubishi Motors Posts Record Sales in the Philippines in FY2023

Apr 24, 2024 13:56 JST

|

NEC Develops High-speed Generative AI Large Language Models (LLM) with World-class Performance

Apr 24, 2024 13:25 JST

|

Fujitsu SX Survey reveals key success factors for sustainability

Apr 23, 2024 10:25 JST

|

Fujitsu and METRON collaborate to drive ESG success: slashing energy costs, boosting productivity with new manufacturing industry solutions

Apr 22, 2024 16:09 JST

|

NEC Strengthens Commitment to Space Industry with Investment in Seraphim Space Venture Fund II

Apr 22, 2024 15:09 JST

|

Soft Space Launches the First and Only JCB Payment Gateway in Malaysia

Apr 22, 2024 15:00 JST

|

TOYOTA GAZOO Racing takes a one-two in Croatian thriller

Apr 22, 2024 10:47 JST

|

First-ever Mazda CX-80 Crossover SUV Unveiled in Europe

Apr 19, 2024 13:50 JST

|

Fujitsu develops technology to convert corporate digital identity credentials, enabling participation of non-European companies in European data spaces

Apr 19, 2024 10:17 JST

|

Mitsubishi Heavy Industries and NGK to Jointly Develop Hydrogen Purification System from Ammonia Cracking Gas

Apr 18, 2024 17:01 JST

|

Toyota Launches All-New Land Cruiser "250" Series in Japan

Apr 18, 2024 13:39 JST

|

More Latest Release >>

|